Hsinchu, Taiwan and Silicon Valley, CA – September 8, 2021 – Andes Technology Corporation (TWSE: 6533), a leading supplier of high efficiency, low-power 32/64-bit RISC-V processor cores and Founding Premier member of RISC-V International, today announced that it has joined Silicon Catalyst’s In-Kind Partner program. Andes Technology will make available a wide range of its RISC-V processors to startups participating in the Silicon Catalyst incubator program.

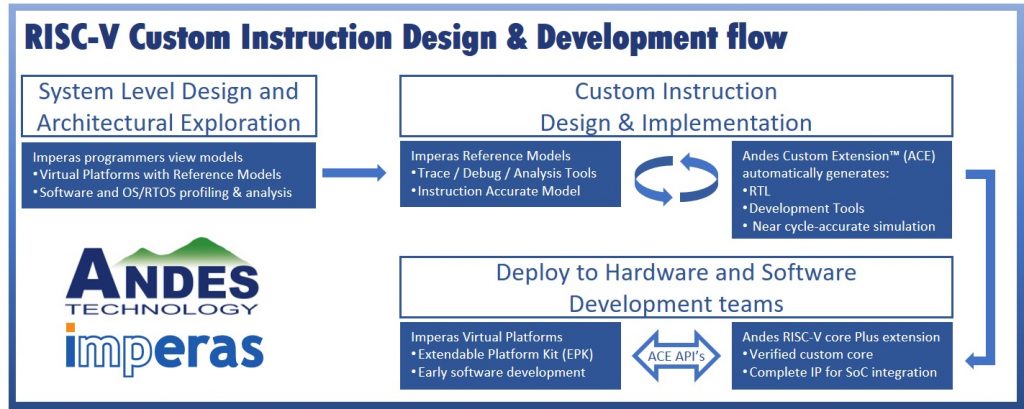

These include all Andes RISC-V offerings between the smallest N22 to its multicore 5-stage pipeline 25 and 27 families with P extension, floating point, L2 cache controller and memory management unit. Incubator startups will also have access to Andes’ AE250 Pre-integrated AHB platform, AE350 Pre-integrated AXI platform, and AndeSight Eclipse-based Integrated Development Environment.

“Andes has been helping a steady stream of new design starts to incorporate our wide range of RISC-V AndesCore™ processors,” said Dr. Charlie Su, President and CTO of Andes Technology. “Silicon start-ups such as those in the Silicon Catalyst incubator program are ideal examples of the new ventures. Many have great products on papers but need the IP and tools to lift their design from the page and implement it in silicon. The Silicon Catalyst incubator and Andes provide them the perfect environment and high efficiency RISC-V CPU IPs to achieve this goal. We are delighted to be part of this endeavor.”

“We applaud Andes’ initiative in expanding the reach and visibility of the RISC-V ISA,” said Calista Redmond, CEO of RISC-V International. “As an open computing platform, the continued growth and adoption of RISC-V depends on a broad ecosystem of hardware and software tools and IP. Andes contributing its silicon-proven RISC-V IP to the Silicon Catalyst incubator will help make it easier for emerging startups to build the next generation of semiconductor applications with RISC-V.”

The mission of Silicon Catalyst is to lower the capital expenses associated with the design and fabrication of silicon-based IC’s, sensors, and MEMS devices. For over seven years, the Silicon Catalyst partner ecosystem has enabled early-stage companies to build complex silicon chips at a fraction of the typical cost. Silicon Catalyst has created a unique ecosystem to provide critical support to semiconductor hardware start-ups, including tools and services from a comprehensive network of In-Kind Partners (IKPs). The Portfolio Companies in the incubator utilize IKP tools and services including design tools, simulation software, design services, foundry PDK access and MPW runs, test program development, tester access, and banking and legal services. Additionally, the startups can tap into the world-class Silicon Catalyst network of advisors and investors.

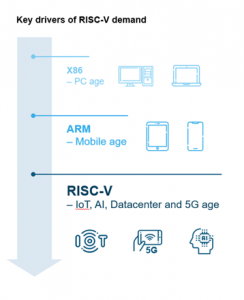

“Adding a tier one RISC-V IP supplier such as Andes Technology; with its broad range of IP, hardware design tools, and integrated software development environment; broadens the selection of design IP and tools our incubator companies have to create with,” said Paul Pickering, Managing Partner at Silicon Catalyst. “Andes’ success with startups in the emerging 5G and AI chip markets demonstrates their understanding of nurturing new ventures building products for markets that are just beginning to field large numbers of new silicon designs. We are pleased to have them join the Silicon Catalyst incubator and look forward to seeing new designs containing their IP.”

About Silicon Catalyst

It’s About What’s Next® – Silicon Catalyst is the world’s only incubator focused exclusively on accelerating solutions in silicon (including IP, MEMS & sensors), building a coalition of in-kind and strategic partners to dramatically reduce the cost and complexity of development. More than 400 startup companies have engaged with Silicon Catalyst since April 2015, with a total of 38 startup and early-stage companies admitted to the incubator. With a world-class network of mentors to advise startups, Silicon Catalyst is helping new semiconductor companies address the challenges in moving from idea to realization. The incubator/accelerator supplies startups with a path to design tools, silicon devices, networking, access to funding, banking and marketing acumen to successfully launch and grow their companies’ novel technology solutions. The Silicon Catalyst Angels was established in July 2019 as a separate organization to provide access to seed and Series A funding for Silicon Catalyst portfolio companies.

More information is available at www.siliconcatalyst.com and www.siliconcatalystangels.com

About Andes Technology

Sixteen years in business and a Founding Premier member of RISC-V International, Andes is a leading supplier of high-performance/low-power 32/64-bit embedded processor IP solutions, and a main force to take RISC-V mainstream. Andes’ fifth-generation architecture AndeStar™ adopted the RISC-V as the base. Its V5 RISC-V CPU families range from tiny 32-bit cores to advanced 64-bit cores with DSP, FPU, Vector, Linux, superscalar, and/or multicore capabilities. The annual volume of Andes-Embedded SoCs has exceeded 2 billion since 2020 and continues to rise. To the end of 2020, the cumulative volume of Andes-Embedded™ SoCs has surpassed 7 billion.

For more information, please visit https://www.andestech.com. Follow Andes on LinkedIn, Twitter, Facebook, and YouTube!

About RISC-V AndesCore™

Andes Technology’s comprehensive CPU includes entry-level, mid-range, high-end, extensible and security families to address the full range of embedded electronics products, especially for connected, smart and green applications. From 2017, Andes expands its product line to RISC-V processors and provides a total solution in V5 family cores, including N22, N25F/NX25F, D25F, A25/AX25, A25MP/AX25MP, A27/AX27/NX27V, A45/D45/N45, AX45/DX45/NX45 and A45MP/AX45MP.

For more information about Andes Technology products, please visit http://www.andestech.com/

Contact Information

Andes Technology – Jonah McLeod , jonahm@andestech.com

Silicon Catalyst – Richard Curtin, richard@siliconcatalyst.com