Rain AI Unveils Andes Technology as Its RISC-V Partner

- Post author:Lee Claire

- Post published:2024-06-03

- Post category:Press Release

Rain AI Licenses Andes AX45MPV and Taps Andes Custom Computing BU to Accelerate Its Launch of Groundbreaking Compute-In-Memory (CIM) Generative AI Solutions

San Francisco, CA, June 03, 2024 – Andes Technology, a leading supplier of high-efficiency, low-power 32/64-bit RISC-V processor cores and Founding Premier member of RISC-V International announces that Rain AI, a pioneer in compute-in-memory (CIM) technology, licensed Andes’ AX45MPV RISC-V vector processor. Rain AI designs novel accelerator solutions, and the two companies are collaborating to accelerate Rain AI’s product roadmap.

As the world economy embraces generative AI to deliver unprecedented benefits to consumers and business alike, energy consumption stands as a significant hurdle regardless of the deployment points, be it the cloud, edge, and especially the smallest sensors. CIM represents the most promising solution to lower the energy footprint by as much as 50X. By performing computations directly in the memory bit-cells, CIM can dramatically reduce the energy required for matrix operations commonly found in machine learning.

However, CIM by itself cannot completely address the vast and growing number of machine learning operators. A RISC-V CPU is ideal for efficient programming and future-proofing of an CIM-based NPU. The RISC-V architecture allows users to add custom instructions to encapsulate the CIM computing blocks, easing software development efforts. Andes automates this instruction customization process with its automated COPILOT compiler.

Mr. Frankwell Lin, Chairman and CEO of Andes, says, “Andes is honored and excited to have Rain AI as its licensee and partner. As the first RISC-V vector processor provider, we see CIM as an inevitable necessity to enable generative AI applications and therefore have focused on CIM customers. To our knowledge, Rain AI has designed one of the most energy efficient matrix multiplication units using digital CIM technology, so we look forward to Rain AI unveiling its breakthrough solutions.”

Mr. William Passo, CEO of Rain AI, echoed this sentiment, stating, “It is rare to see a vendor who shares the same market and technology vision as us, has best-in-class RISC-V solutions for our technology needs, and can commit resources to help us accelerate our roadmap to significantly reduce the energy required for AI. Running the most advanced models in any form factor is the future of AI, and we are now one step closer with Andes.”

Indeed, Rain AI further taps into Andes’ Custom Computing Business Unit (CCBU) to help accelerate the integration of Andes AX45MPV and the ACE/COPILOT instruction customization with on-site and remote consulting services. Andes’ CCBU is a small team of experts tasked to perform complex customizations and integrations for a few promising cutting-edge licensees.

Both companies can share that AX45MPV and Andes’ unique RISC-V instruction customization solution, ACE/COPILOT both play pivotal roles to complement Rain AI’s groundbreaking CIM hardware, compiler, and runtime software to deliver scalable ML solutions for a variety of deployment points. Rain AI will unveil its accelerator solution in early 2025.

About Andes Technology

Nineteen years in business and a Founding Premier member of RISC-V International, Andes is a publicly-listed company (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099) and a leading supplier of high-performance/low-power 32/64-bit embedded processor IP solutions, and the driving force in taking RISC-V mainstream. Its V5 RISC-V CPU families range from tiny 32-bit cores to advanced 64-bit Out-of-Order processors with DSP, FPU, Vector, Linux, superscalar, functional safety and/or multi/many-core capabilities. By the end of 2023, the cumulative volume of Andes-Embedded™ SoCs has surpassed 14 billion. For more information, please visit https://www.andestech.com. Follow Andes on LinkedIn, Twitter, Bilibili and YouTube! !

About Rain AI

Rain AI’s mission is to enable advanced and abundant AI everywhere by building the world’s most efficient AI hardware. It creates flexible solutions for generative AI inference and training utilizing novel compute-in-memory CIM technology, RISC-V processing cores, advanced packaging techniques, and optimized ML algorithms. By co-designing hardware with leading AI models, Rain AI sets new standards in AI efficiency and performance. Rain AI investors include Sam Altman, Dan Gross, and Y Combinator. For further information, visit http://www.rain.ai.

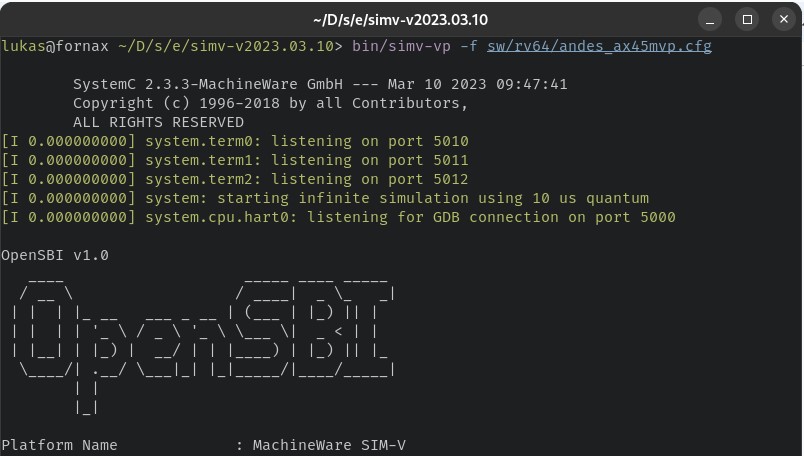

Figure 1: Invoking SIM-V with the AX45MPV configuration.

Figure 1: Invoking SIM-V with the AX45MPV configuration.