Seven Years of Uninterrupted Growth: Andes Technology Achieves Milestone Annual Revenue Exceeding NT$1 Billion

- Post author:Hsiaoling Lin

- Post published:2024-03-21

- Post category:Press Release

Andes Technology Is the No. 1 Provider of RISC-V CPU IP According to the SHD Marketing Report

【 Mar. 21, 2024 – Hsinchu, Taiwan】Since its IPO in 2017, Andes Technology (TWSE:6533) has established itself as a leader in the CPU IP sector, achieving a fivefold increase in sales over the past seven years. Andes has invested capital and R&D manpower to accelerate the launch of high-end products to ensure long-term competitiveness and maintain market leadership. It is expected that a competitive product portfolio will create the next wave of revenue peaks.

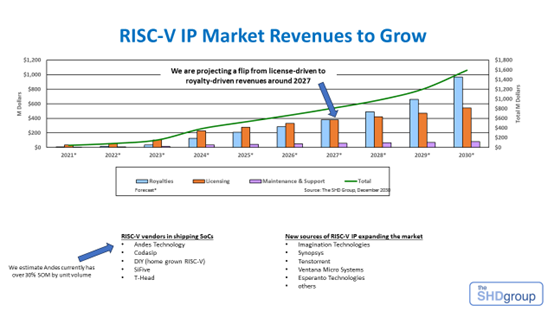

(Image Source: SHD 2024 RISC-V Market Analysis)

With close monitoring of market dynamics and technology trends and decisive decision-making, Andes has strategically positioned the company to adeptly navigate challenges and seize emerging opportunities, such as bringing innovations in its proprietary AndeStar™ V3 ISA to the RISC-V based AndeStar™ V5 ISA in 2016. In 2023, even when the whole industry was still under inventory pressure, Andes surpassed a significant total shipment milestone of 14 billion Andes-Embedded™ SoCs. According to the SHD marketing report released on Jan 2024, Andes has secured an impressive 30% market share of RISC-V based chip shipping volume through its worldwide customers and is the number one provider of RISC-V CPU IP.

In 2023, the diverse product portfolio offered by Andes has resonated exceptionally well with the market and enabled its sustained growth. Andes has successfully launched the groundbreaking vector processor-AX45MPV, and the industry-revolutionizing automotive ISO 26262 fully certified core N25F-SE. More recently, Andes ventured into the application processor market with the launch of its cutting-edge out-of-order (OOO) processor AX65. AndesCore™ D23 and N225 are also released for the compact, performant, and secure applications. Besides the CPU IPs, Andes has also established a new product line, AndesAIRE™ or Andes AI Runs Everywhere, which offers a comprehensive hardware and software solution designed for edge and end-point inference.

Andes’s unwavering commitment to customer satisfaction has fostered robust relationships with its customers and fortified its market position. The addressable market segments of Andes products span a wide spectrum, encompassing AI/ML, 5G communications, FPGAs, image processing, IoT, MCU/MPU, sensors, storage, TDDI, and wireless connectivity.

Looking ahead, Andes would continue its dedication to innovations, customer satisfaction, and continual adaptation in the dynamic CPU IP licensing market. Below are a set of key drivers underpinning Andes’ growth:

Expansion of AI and HPC Applications: The ongoing surge in demand for AI and High-Performance Computing (HPC) applications, coupled with the requirements for specialized SoC, serves as one of the primary catalysts for Andes. Offering processors enhanced with ACE™ (Andes Automated Custom Extension) to meet the stringent requirements of AI and HPC workloads has significantly contributed to Andes’ market growth.

Increasing Demands for Automotive-Grade (ISO 262626) SoC: As the automotive industry continues to advance, there is a rising need for Automotive-Grade SoCs compliant with the ISO 262626 standard. Andes has seized this trend and is actively catering to the increasing demands for automotive-grade solutions. By offering processors designed to meet the stringent safety and reliability requirements of the automotive sector, Andes is well-positioned to capitalize on this growing market segment, further enhancing its success and market penetration.

Maturity of the RISC-V Ecosystem: By actively participating in the RISC-V International and community with the highest RVI membership and Summit sponsorship, Andes contributes to the RISC-V ecosystem’s fast expansion. Through this effort, Andes remains at the forefront of RISC-V development, fostering a positive cycle benefiting both the company and the ecosystem.

Rise of Multi-Core Heterogeneous SoC: The growing complexity of modern applications, spanning various domains like AIoT, edge computing, and data centers, has led to the rise in multi-core heterogeneous System-on-Chips (SoCs). Andes’ strategic focus on developing a diverse product portfolio aligns seamlessly with the demands of multi-core heterogeneous SoCs. These processors offer the performance and flexibility needed to address the contemporary applications’ requirements.

“Andes Technology’s journey of consistent growth over the past seven years is a testimony to our unwavering determination of staying ahead of industry trends and commitment to customers,” said Frankwell Lin, the Chairman, and CEO of Andes Technology. “We remain dedicated to shaping the future of the CPU IP licensing market with cutting-edge solutions.”

“As Andes charts our roadmap for the future, with ‘Driving Innovations’ as our motto, on one hand, we are developing high-end products that push the boundaries of performance,” remarked Dr. Charlie Su, the CTO and President. “On the other hand, we continue to deliver strong compact processors for power-efficiency and security. Aligning our expertise with the evolving needs of this dynamic industry, our talented team and effective collaboration with customers will continue to drive us forward, shaping the future of high-performance and high-efficiency computing, complying to strict safety demands in automotive SoC, and addressing the ever-emerging AI requirements.”

About ANDES RISC-V CON

ANDES RISC- V CON is the annual RISC-V technology forum hosted by Andes Technology and sponsored by partners. In 2024, the San Jose session will be held in Doubletree by Hilton Hotel on June 11. The 2024 theme is “Deep Dive into Automotive/AI/Application Processing and Security Trends.” It will introduce the flexible RISC-V processors that changes the face of emerging computing and share how Andes assists the RISC-V ecosystem in implementing diversified applications of innovative technologies. Four popular application areas will be focused on: AI/ML, automotive electronics, application processing and security. Many ecosystem partners are invited to give talks and on-site demonstrations. For free registration, please see the official website of Andes RISC-V CON https://www.andestech.com/Andes_RISC-V_CON_2024_US/

About Andes Technology

Nineteen years in business and a Founding Premier member of RISC-V International, Andes is a publicly-listed company (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099), a leading supplier of high-performance/ low-power 32/64-bit embedded processor IP solutions, and the driving force in taking RISC-V mainstream. Andes’ fifth-generation AndeStar™ architecture adopted the RISC-V as the base. Its V5 RISC-V CPU families range from tiny 32-bit cores to advanced 64-bit Out-of-Order processors with DSP, FPU, Vector, Linux, superscalar, functional safety, and/or multicore capabilities. By the end of 2023, the cumulative volume of Andes-Embedded™ SoCs has surpassed 14 billion. For more information, please visit https://www.andestech.com. Follow Andes on LinkedIn, Facebook, X, Bilibili and YouTube!