Andes Technology Steps Up to Premier Membership in RISC-V International; Greatly Expanding its U.S. R&D and Field Application Engineering Staffing

- Post author:Rachel Miaou

- Post published:2020-06-08

- Post category:Press Release

SAN JOSE CA – June 8, 2020 – Andes Technology Corporation (TWSE: 6533), a leading supplier of high efficiency, low-power 32/64-bit RISC-V processor cores and founding member of RISC-V International, announces its Premier membership in the organization. Andes President Frankwell Lin takes his seat on the RISC-V International Board. Andes CTO and Executive VP Charlie Su becomes Vice Chair of the RISC-V International Technical Steering Committee. The company will take an active role in the upcoming 2020 RISC-V Summit. Andes’ increased participation in RISC-V International reflects the growing demand for its broad family of RISC-V cores including its highly demanded RISC-V cores with DSP or vector extensions. As a result, Andes Technology is growing its U.S. footprint by expanding its R&D and applications engineering staffing several fold.

“We’ re seeing a rapid expansion in our RISC-V business thanks to system-on-chip designers’ eager adoption of the open source RISC-V CPU instruction set architecture,” said Andes President Frankwell Lin. “Our RISC-V CPU IPs offerings in 2018 have grown three-fold to cover a wide spectrum of applications from IoT devices at the edge to compute intensive servers in the cloud. Last year, our RISC-V solutions have already represented the major share of Andes’ business.”

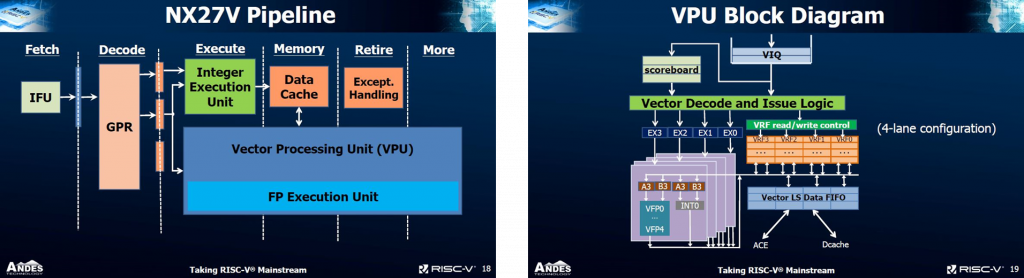

“The Andes growing R&D team worldwide has demonstrated its engineering ingenuity in our expanding RISC-V offerings,” said Andes Technology CTO and Executive VP Charlie Su. “We developed powerful internal design tools to quickly architect, design, and verify a new processor core. This design flow allows us to rapidly launch a new product to meet rapidly evolving market demand. The development of Andes NX27V RISC-V core with vector extension is a prime example. NX27V is the world first commercial RISC-V vector processor. Andes engineering team had launched and integrated it into customer’s SoC design in a short time. Andes had productized this CPU design automation expertise in the form of our Andes Custom Extension™ (ACE) and COPILOT tool that allows SoC designers to add custom instructions to our RISC-V CPU to make it unique to their solution.”

“Andes USA’s growing footprint has included expanding R&D staffing as well as sales and field application engineering,” said Emerson Hsiao, Andes Technology USA Corp. Senior VP. “In spite of the current constrained business atmosphere, Andes USA continues to experience strong demand for our RISC-V IP solutions. This is in no small part due to Andes’ powerful design automation tools Andes Custom Extension™ and COPILOT. They allow designers to create custom instructions to greatly accelerate performance while drastically reducing power consumption. This capability contributed significantly to the business growth for Andes USA. We continue to look for talented individuals to help us with our growth.”

About Andes Technology Corp.

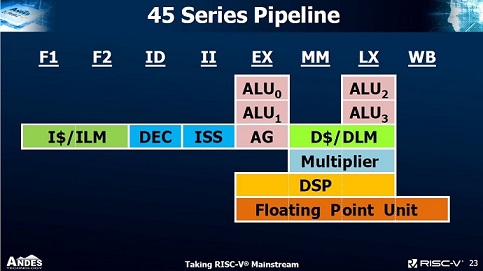

Andes Technology Corporation is a world class creator of innovative high-performance/low-power 32/64-bit processor cores and associated development environment that serves the rapidly growing global market for embedded system applications. As the founding Premier member of RISC-V International, Andes is the first mainstream CPU vendor that adopted the RISC-V as the base of its fifth-generation architecture, the AndeStar™ V5. To meet the demanding requirements of today’s electronic devices, Andes delivers highly configurable and performance-efficient CPU cores. They come with full-featured integrated development environment and comprehensive software/hardware solutions to help designers innovate their SoCs in a shorter time to market. In 2019, the volume of SoCs Embedded with Andes CPUs surpassed the 1.5-billion mark. Andes Technology’s comprehensive RISC-V CPU families range from the entry-level 32-bit N22, mid-range 32-bit N25F/D25F/A25/A27 and 64-bit NX25F/AX25/AX27, to the high-end multicore A(X)25MP and vector processor NX27V. Coming soon is the superscalar 45 series.